Pezy Computing Apresenta Processador MIMD Massivo, o SC4s, no Nó de 5nm da TSMC

Pontos principais

- A Pezy Computing introduziu o SC4s, um processador de grande die de 5nm construído no processo da TSMC.

- O chip adota uma arquitetura de Múltiplas Instruções Múltiplos Dados (MIMD), enfatizando a operação independente do núcleo.

- Simulações sugerem que o SC4s oferece mais do que o dobro da eficiência de energia em cargas de trabalho DGEMM em comparação com o design SC3 anterior.

- Um aumento de desempenho quatro vezes maior é projetado para o algoritmo de alinhamento de genoma Smith-Waterman.

- O tamanho do die é de aproximadamente 556 mm², significativamente maior do que os CPUs de consumo típicos.

- A Pezy planeja um sucessor, Pezy 5, visando um processo sub-3nm com uma janela de lançamento provisória de 2027.

- As alegações de desempenho são atualmente baseadas em simulações, aguardando validação de hardware independente.

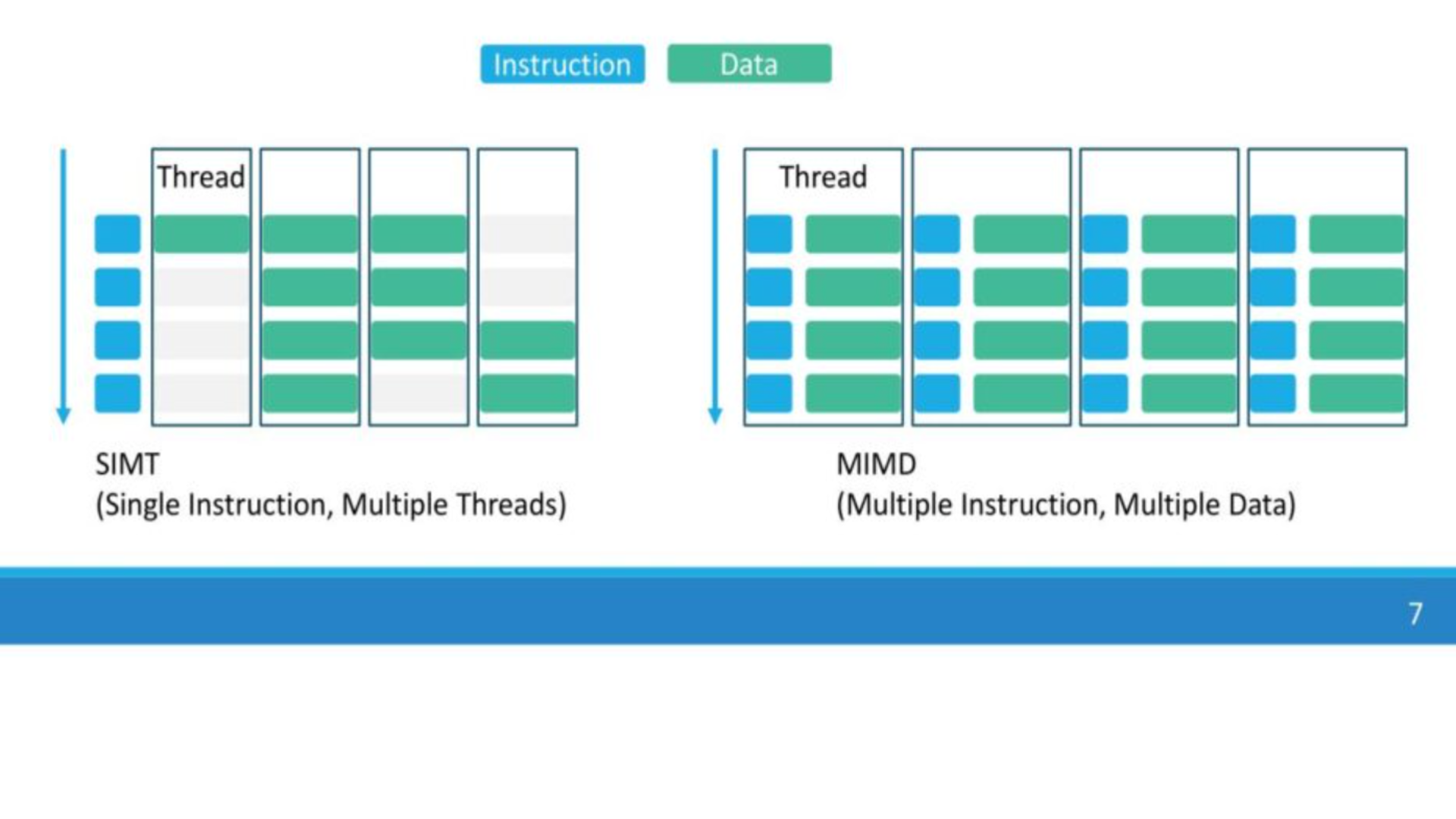

Pezy Computing apresentou seu processador SC4s, um chip grande de 5nm que adota uma arquitetura de Múltiplas Instruções Múltiplos Dados (MIMD) em vez da abordagem SIMD mais comum. O chip, fabricado pela TSMC, possui um die de aproximadamente 556 mm² e visa entregar centenas de núcleos semi-autônomos que podem operar independentemente.

Desvio Estratégico da Pezy Computing para MIMD

Em uma recente apresentação da indústria, a empresa japonesa Pezy Computing introduziu o processador SC4s, marcando uma clara mudança de direção em relação ao foco da indústria em arquiteturas de Dado Múltiplo de Instrução Única (SIMD). Em vez disso, a Pezy está defendendo a arquitetura MIMD, uma filosofia de design que trata cada núcleo como uma unidade semi-autônoma, semelhante a uma coleção de estados, prefeituras, cidades e vilas que atuam independentemente em vez de seguir uma autoridade central única.

Características Físicas e Fabricação

O SC4s é construído no processo de 5nm da TSMC e é notável por sua pegada física incomumente grande. O die mede cerca de 556 mm², tornando-o consideravelmente maior do que a maioria dos processadores de consumo ou de workstation. A ênfase da Pezy não está em minimizar a área de silício, mas em testar se o paralelismo maciço pode superar o custo de um die maior.

Ganhos de Desempenho Projetados

A Pezy liberou dados de simulação em vez de benchmarks de silício. Em comparação com seu antecessor, o SC3, o SC4s é projetado para entregar mais do que o dobro da eficiência de energia em uma carga de trabalho de multiplicação de matriz densa (DGEMM). Em outra simulação, o processador alcançou um aumento de desempenho quase quatro vezes maior no algoritmo Smith-Waterman, um componente-chave do alinhamento de sequências de genoma.

Filosofia de Design e Perspectiva de Mercado

A empresa argumenta que as cargas de trabalho futuras exigirão cada vez mais o tratamento de threads independentes, tornando os designs baseados em MIMD mais adequados para domínios especializados. Embora a abordagem possa ser impraticável para uma adoção ampla de consumidores, a Pezy acredita que certos nichos de alto desempenho possam justificar a escala de centenas ou milhares de núcleos independentes.

Roadmap Futuro

Embora o SC4s ainda esteja em desenvolvimento, a Pezy já está olhando para um processador de quinta geração, provisoriamente chamado de Pezy 5. Este sucessor deve migrar para um nó de processo de 3nm ou menor, com uma janela de lançamento provisória definida para 2027. Observadores da indústria notam que esses prazos muitas vezes mudam devido a desafios técnicos e econômicos.

Ceticismo da Indústria e Validação

Como as alegações de desempenho são baseadas em simulações, testes independentes serão essenciais para validar os ganhos projetados. Historicamente, projeções ousadas no desenvolvimento de semicondutores nem sempre se alinharam com os resultados medidos uma vez que o hardware é enviado, provocando um otimismo cauteloso entre os analistas.