Pezy Computing Unveils Massive MIMD Processor, the SC4s, on TSMC’s 5nm Node

Key Points

- Pezy Computing introduced the SC4s, a large‑die 5nm processor built on TSMC’s process.

- The chip adopts a Multiple Instructions Multiple Data (MIMD) architecture, emphasizing independent core operation.

- Simulations suggest the SC4s offers more than double the power efficiency on DGEMM workloads versus the prior SC3 design.

- A four‑fold performance boost is projected for the Smith‑Waterman genome‑alignment algorithm.

- The die size is roughly 556 mm², significantly larger than typical consumer CPUs.

- Pezy plans a successor, Pezy 5, targeting a sub‑3nm process with a tentative 2027 release window.

- Performance claims are currently simulation‑based, awaiting independent hardware validation.

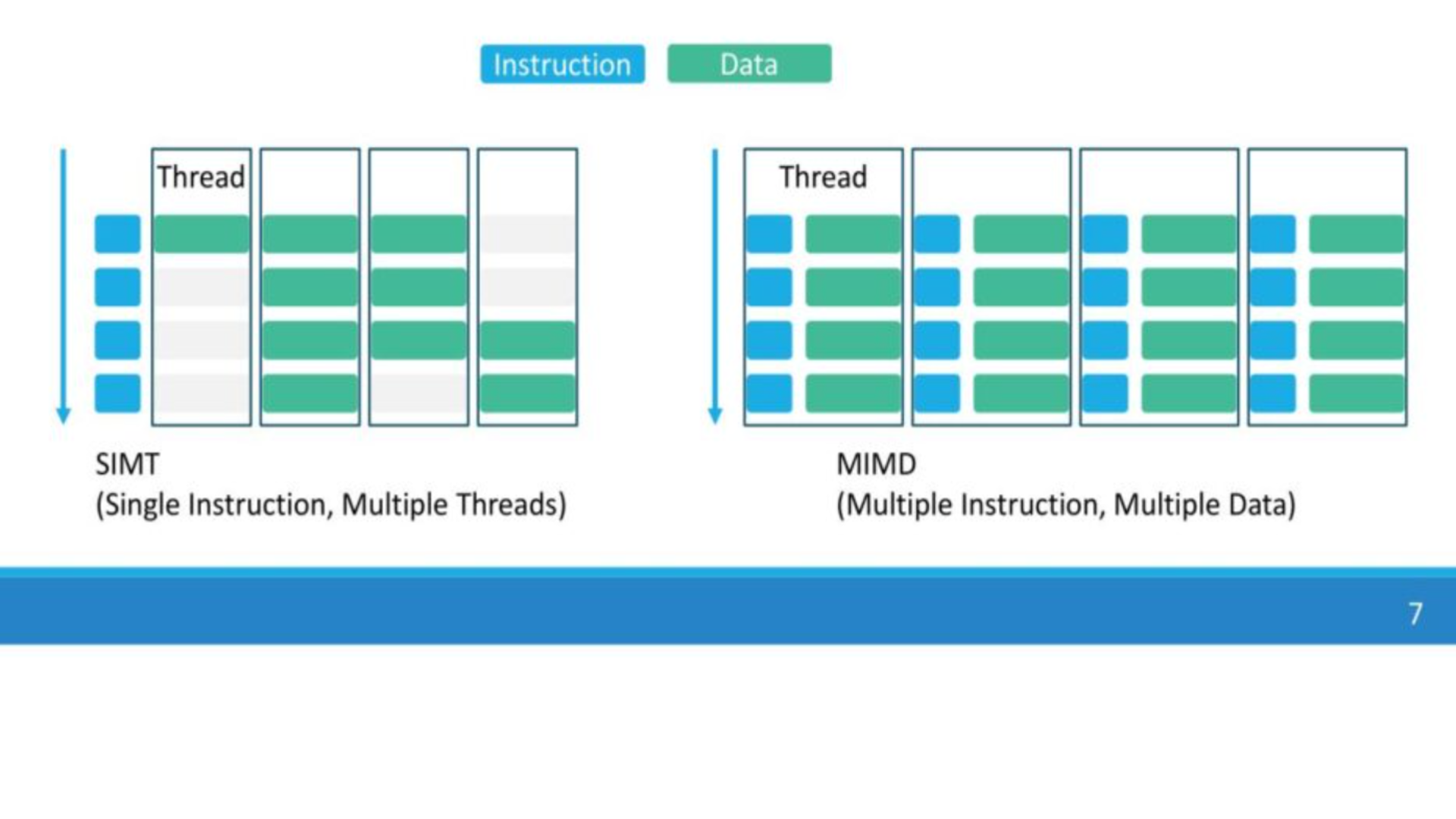

Pezy Computing presented its SC4s processor, a large‑die, 5nm chip that embraces a Multiple Instructions Multiple Data (MIMD) design rather than the mainstream SIMD approach. The chip, fabricated by TSMC, features a die of roughly 556 mm² and aims to deliver hundreds of semi‑autonomous cores that can operate independently. Simulated workloads, including DGEMM and the Smith‑Waterman genome‑alignment algorithm, show substantial gains in power efficiency and performance compared with Pezy’s earlier SC3 design. While the results are still based on simulations, the company plans to move toward a successor using a sub‑3nm process.

Pezy Computing’s Strategic Shift to MIMD

At a recent industry showcase, the Japanese firm Pezy Computing introduced the SC4s processor, marking a clear departure from the industry‑wide focus on Single Instruction Multiple Data (SIMD) architectures. Instead, Pezy is championing Multiple Instructions Multiple Data (MIMD), a design philosophy that treats each core as a semi‑autonomous unit, akin to a collection of states, prefectures, cities, and villages that act independently rather than following a single central authority.

Physical Characteristics and Manufacturing

The SC4s is built on TSMC’s 5nm process and is notable for its unusually large physical footprint. The die measures around 556 mm², making it considerably larger than most consumer or workstation processors. Pezy’s emphasis is not on minimizing silicon area but on testing whether massive parallelism can outweigh the cost of a larger die.

Projected Performance Gains

Pezy released simulation data rather than silicon benchmarks. Compared with its predecessor, the SC3, the SC4s is projected to deliver more than double the power efficiency on a dense matrix multiplication workload (DGEMM). In another simulation, the processor achieved nearly a four‑fold performance increase on the Smith‑Waterman algorithm, a key component of genome‑sequence alignment.

Design Philosophy and Market Outlook

The company argues that future workloads will increasingly demand independent thread handling, making MIMD‑based designs more suitable for specialized domains. While the approach may be impractical for broad consumer adoption, Pezy believes that certain high‑performance niches can justify the scale of hundreds or thousands of independent cores.

Future Roadmap

Even as the SC4s remains under development, Pezy is already looking ahead to a fifth‑generation processor, tentatively called Pezy 5. This successor is expected to move to a 3nm or smaller process node, with a tentative release window set for 2027. Industry observers note that such timelines often shift due to technical and economic challenges.

Industry Skepticism and Validation

Because the performance claims are based on simulations, independent testing will be essential to validate the projected gains. Historically, bold projections in semiconductor development have not always aligned with measured results once hardware ships, prompting cautious optimism among analysts.